# Lecture Notes in Computer Science

5026

Commenced Publication in 1973

Founding and Former Series Editors:

Gerhard Goos, Juris Hartmanis, and Jan van Leeuwen

#### **Editorial Board**

**David Hutchison**

Lancaster University, UK

Takeo Kanade

Carnegie Mellon University, Pittsburgh, PA, USA

Josef Kittler

University of Surrey, Guildford, UK

Jon M. Kleinberg

Cornell University, Ithaca, NY, USA

Alfred Kobsa

University of California, Irvine, CA, USA

Friedemann Mattern

ETH Zurich, Switzerland

John C. Mitchell

Stanford University, CA, USA

Moni Naor

Weizmann Institute of Science, Rehovot, Israel

Oscar Nierstrasz

University of Bern, Switzerland

C. Pandu Rangan

Indian Institute of Technology, Madras, India

Bernhard Steffen

University of Dortmund, Germany

Madhu Sudan

Massachusetts Institute of Technology, MA, USA

Demetri Terzopoulos

University of California, Los Angeles, CA, USA

Doug Tygar

University of California, Berkeley, CA, USA

Gerhard Weikum

Max-Planck Institute of Computer Science, Saarbruecken, Germany

Fabrice Kordon Tullio Vardanega (Eds.)

# Reliable Software Technologies – Ada-Europe 2008

13th Ada-Europe International Conference on Reliable Software Technologies Venice, Italy, June 16-20, 2008 Proceedings

#### Volume Editors

Fabrice Kordon

Université Pierre et Marie Curie

Laboratoire d'Informatique de Paris 6

Modeling and Verification

CNRS UMR 7606, 4 place Jussieu, 75252 Paris Cedex 05, France

E-mail: Fabrice.Kordon@lip6.fr

Tullio Vardanega University of Padua Department of Pure and Applied Mathematics via Trieste 63, 35121 Padua, Italy E-mail: tullio.vardanega@math.unipd.it

Library of Congress Control Number: 2008927854

CR Subject Classification (1998): D.2, D.1, D.3, C.2.4, K.6

LNCS Sublibrary: SL 2 – Programming and Software Engineering

ISSN 0302-9743

ISBN-10 3-540-68621-5 Springer Berlin Heidelberg New York ISBN-13 978-3-540-68621-7 Springer Berlin Heidelberg New York

This work is subject to copyright. All rights are reserved, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, re-use of illustrations, recitation, broadcasting, reproduction on microfilms or in any other way, and storage in data banks. Duplication of this publication or parts thereof is permitted only under the provisions of the German Copyright Law of September 9, 1965, in its current version, and permission for use must always be obtained from Springer. Violations are liable to prosecution under the German Copyright Law.

Springer is a part of Springer Science+Business Media

springer.com

© Springer-Verlag Berlin Heidelberg 2008 Printed in Germany

Typesetting: Camera-ready by author, data conversion by Scientific Publishing Services, Chennai, India Printed on acid-free paper SPIN: 12275687 06/3180 5 4 3 2 1 0

### **Preface**

The 13<sup>th</sup> edition of the International Conference on Reliable Software Technologies (Ada-Europe 2008) marked its arrival in Italy by selecting the splendid venue of Venice. It did so after having been hosted twice in Switzerland, Spain and the UK (Montreux for its inauguration in 1996 and Geneva in 2007; Santander in 1999 and Palma de Mallorca in 2004; London in 1997 and York in 2005), and having visited Sweden (Uppsala, 1998), Germany (Potsdam, 2000), Belgium (Leuven, 2001), Austria (Vienna, 2002), France (Toulouse, 2003) and Portugal (Porto, 2006). It was certainly high time that the conference came to Italy!

The conference series, which is run and sponsored by Ada-Europe, chooses its yearly venue following two driving criteria: to celebrate the activity of one of its national member societies in a particular country, and/or to facilitate the formation, or the growth, of a national community around all aspects of reliable software technologies. The success of this year's conference, beside the richness of its technical and social program, will thus be measured by its lasting effects. We can only hope that the latter will be as good and vast as the former!

Owing to the absence of a national society associated with Ada-Europe in Italy, the organization of the conference was technically sustained by selected members of the Board of Ada-Europe, its governing body, with some invaluable local support. The Board thus faced the very serious challenge of having to keep up with the high standard of previous Ada-Europe conferences. With all aspects of the organization behind us, we can be satisfied that the success of the conference was confirmed, continued and increased.

The conference took place on June 16–20, 2008 and featured a rich, dense and attractive program. Following its usual style the conference spanned a full week, with 10 tutorials offered on Monday and Friday, and a technical program from Tuesday to Thursday, which included 3 keynote talks, 20 peer-reviewed papers, 12 industrial presentations, a special session on software engineering education, the traditional vendor session and the accompanying industrial exhibition. Let us now look at the highlights of the conference program in some more detail.

The keynote talks were given by eminent and inspired speakers:

- Alberto Sangiovanni-Vincentelli (University of California at Berkeley, USA), a most authoritative member of the embedded systems community worldwide, delivered a talk entitled: Embedded Software Design: Art or Science?

- Robert Dewar (New York University, USA), a renowned expert in programming technologies and a talented public speaker, discussed where programming languages are expected to go next in a talk evocatively entitled: Lost in Translation.

- Christian Queinnec (Université Pierre et Marie Curie, Paris, France), a leading researcher in programming language semantics and the programming of the Web, explored the inner heart of Service-Oriented Architecture in a talk entitled: Three Ways to Improve SOA Reliability.

Submissions to the peer-reviewed track of the conference came from 15 countries worldwide, which caused a fairly competitive selection process that resulted in the making of 7 technical sessions on topics ranging from formal verification to real-time systems via concurrency, embedded systems, language technologies, model-driven engineering and applications of Petri Nets. The conference proceedings published in this volume fully cover this track of the conference.

The tutorial program featured a rich variety of topics, all presented by recognized domain experts, in close match with the core scope of the conference, as follows:

- AADL: Architecture Analysis and Design Language, Jean-Pierre Rosen (Adalog, France)

- The Best of Ada 2005, John Barnes (John Barnes Informatics, UK)

- Object-Oriented Programming in Ada 2005, Matthew Heaney (On2 Technologies, USA)

- Preserving Model-Asserted Properties at Run Time for High-Integrity Systems,

Tullio Vardanega (University of Padua, Italy) and Juan Antonio de la Puente (Technical University of Madrid, Spain)

- Technical Basis of Model Driven Engineering, and

- Verification Techniques for Dependable Systems, both by William Bail (The MITRE Corporation, USA)

- A Practical Introduction to Model-Driven Software Development Using Eclipse, Cristina Vicente-Chicote and Diego Alonso-Cáceres (Universidad Politécnica de Cartagena, Spain)

- Languages for Safety-Critical Software: Issues and Assessment, Benjamin Brosgol (AdaCore, USA)

- Service-Oriented Architecture Concepts and Implementations, Ricky Sward (The MITRE Corporation, USA)

- Real-Time Scheduling Analysis of Ada Applications, Frank Singhoff (University of Brest, France).

The industrial track received the largest number of submissions since its inception in 2005. We read this as a twofold token of the thriving activity of the high-integrity industry worldwide and of the need of its representatives to meet with researchers and practitioners in reliable software technologies. The conference program included the following industrial talks:

- A Discussion on the U.S. Federal Aviation Administration's Use of and Experiences with Ada, Including the Current Modernization Efforts, Jeffrey O'Leary (FAA, USA) and Alok Srivastava (Northrop Grumman Corporation, USA)

- Experiences Developing the Flight Services Component of the ERAM System, Howard Ausden (Lockheed Martin, USA)

- Challenges in Implementing a Ravenscar Runtime in an ARINC 653 Partition, Jean-Pierre Fauche and Tom Grossman (Aonix, France)

- Binary Data Comparison Automation, Matt Mark (Lockheed Martin, USA)

- Industrial Feedback on the Separation of Functional and Real-Time Constraints, and Object Orientation for Embedded Application, Mathieu Le Coroller, Gérald Garcia (Thales Alenia Space, France)

- Advanced Real-Time Analysis in ASSERT Application on Satellite Central Flight Software, Dave Thomas, Jean-Paul Blanquart (EADS/Astrium Satellites, France), Marco Panunzio (Università di Padova, Italy)

- Porting Naval Command and Control Systems to Ada 2005, Jeff Cousins (BAE Systems, UK)

- Distributed Status Monitoring and Control Using Remote Buffers and Ada 2005, Brad Moore (General Dynamics, Canada)

- A Comparison of Industrial Coding Rules, Jean-Pierre Rosen (Adalog, France)

- Growing a Tree that Lives Forever: Automatic Storage Management and Persistence of Complex Data Structures, S. Tucker Taft (SoftCheck, USA)

- Exceptionally Safe, Arnaud Charlet, Cyrille Comar, Franco Gasperoni (AdaCore, France)

- Genesis. Automation, via Generation, via ASIS, of Tests of Ada Software, Mário A. Alves, Nuno Almeida (Critical Software, Portugal).

The special session on software engineering education hosted four talks and a lively panel discussion. The following presentations were given:

- A Rational Approach to Software Engineering Education or: Java Considered Harmful, Ed Schonberg, Robert Dewar (New York University, USA)

- Ada and Software Engineering Education: One Professor's Experiences, John W. McCormick (University of Northern Iowa, USA)

- Is Ada Education Important?, Jean-Pierre Rosen (Adalog, France)

- Use of Ada in a Student CubeSat Project, Carl Brandon (Vermont Technical College, USA).

Reports on the tutorial program, the industrial track and the special session on software engineering education will all be published in issues of the Ada User Journal produced by Ada-Europe.

Before closing this preface, we would like to acknowledge the work of those who contributed to the success of the conference, in various roles, moments and levels of visibility. First and foremost we want to express our gratitude to the authors of all presentations included in the program: the success of the conference was also largely theirs. We would also like to thank the members of the program committee at large: while they operated mostly in the background, their effort was crucial to keeping the level of the program quality as high as expected by soliciting worthwhile submissions as well as by carrying out the critical task of peer-reviewing. A smaller group of people accomplished the year-long task of following the preparation, construction and execution of the conference program as a whole. They deserve to be thanked for their effort and dedication: the Local Chair, Sabrina De Poli; the Publicity Chair, Dirk Craeynest; the Exhibition Chair, Ahlan Marriott; and the Tutorial Chair, Jorge Real.

We, who had the privilege of running the organization team, do hope that the attendees enjoyed the conference, in both its technical and social program, as much as we enjoyed coordinating it. We close this volume with the confidence of a job well done and the satisfaction of a thoroughly enjoyable experience.

# **Organization**

#### **Conference Chair**

Tullio Vardanega, Università di Padova, Italy

# **Program Co-chairs**

Tullio Vardanega, Università di Padova, Italy Fabrice Kordon, Université P. & M. Curie, France

### **Tutorial Chair**

Jorge Real, Universidad Politécnica de Valencia, Spain

### **Exhibition Chair**

Ahlan Marriott, White Elephant GmbH, Switzerland

# **Publicity Chair**

Dirk Craeynest, Aubay Belgium & K.U. Leuven, Belgium

### **Local Chair**

Sabrina De Poli, Sistema Congressi srl, Italy

# **Ada-Europe Conference Liaison**

Fabrice Kordon, Université P. & M. Curie, France

# **Sponsoring Institutions**

AdaCore Praxis High-Integrity Systems

Aonix Rapita Systems Ltd

Ellidiss Software Telelogic

Dipartimento di Matematica Pura ed Applicata, Università di Padova, Italy

### **Program Committee**

Nabil Abdennadher, University of Applied Sciences, Switzerland Alejandro Alonso, Universidad Politécnica de Madrid, Spain Johann Blieberger, Technische Universität Wien, Austria Maartin Boasson, University of Amsterdam, The Netherlands Bernd Burgstaller, Yonsei University, Korea Dirk Craevnest, Aubay Belgium & K.U. Leuven, Belgium Alfons Crespo, Universidad Politécnica de Valencia, Spain Juan A. de la Puente, Universidad Politécnica de Madrid, Spain Raymond Devillers, Université Libre de Bruxelles, Belgium Michael González Harbour, Universidad de Cantabria, Spain José Javier Gutiérrez, Universidad de Cantabria, Spain Serge Haddad, Université Paris-Dauphine, France Andrew Hately, Eurocontrol CRDS, Hungary Jerôme Hugues, Télécom Paris, France Günter Hommel, Technische Universität Berlin, Germany Hubert Keller, Institut für Angewandte Informatik, Germany Yvon Kermarrec, ENST Bretagne, France Fabrice Kordon, Université Pierre & Marie Curie, France Albert Llemosí, Universitat de les Illes Balears, Spain Kristina Lundqvist, MIT, USA Franco Mazzanti, ISTI-CNR Pisa, Italy John McCormick, University of Northern Iowa, USA Stephen Michell, Maurya Software, Canada Javier Miranda, Universidad Las Palmas de Gran Canaria, Spain Daniel Moldt, Universität Hamburg, Germany Laurent Pautet, Télécom Paris, France Laure Petrucci, LIPN, Université Paris 13, France Luís Miguel Pinho, Polytechnic Institute of Porto, Portugal Erhard Plödereder, Universität Stuttgart, Germany Jorge Real, Universidad Politécnica de Valencia, Spain Alexander Romanovsky, University of Newcastle upon Tyne, UK Jean-Pierre Rosen, Adalog, France José Ruiz, AdaCore, France Lionel Seinturier, Université de Lille, France Man-Tak Shing, Naval Postgraduate School, USA Alok Srivastava, Northrop Grumman, USA Tullio Vardanega, Università di Padova, Italy Andy Wellings, University of York, UK Jürgen Winkler, Friedrich-Schiller-Universität, Germany

Luigi Zaffalon, University of Applied Sciences, Switzerland

# **Industrial Committee**

Guillem Bernat, Rapita Systems, UK Olivier Devuns, Aonix, France Franco Gasperoni, AdaCore, France Rei Stråhle, Saab Systems, Sweden Dirk Craeynest, Ada-Europe (Vice-President), Belgium Tullio Vardanega, Ada-Europe (President), Italy

# Table of Contents

| A New Approach to Memory Partitioning in On-Board Spacecraft Software                           | 1   |

|-------------------------------------------------------------------------------------------------|-----|

| Santiago Urueña, José A. Pulido, Jorge López,<br>Juan Zamorano, and Juan A. de la Puente        |     |

| Design and Development of Component-Based Embedded Systems for Automotive Applications          | 15  |

| On the Timed Automata-Based Verification of Ravenscar Systems Iulian Ober and Nicolas Halbwachs | 30  |

| Operational Semantics of Ada Ravenscar                                                          | 44  |

| Practical, Fast and Simple Concurrent FIFO Queues Using Single Word Synchronization Primitives  | 59  |

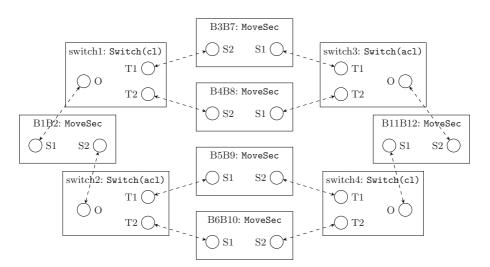

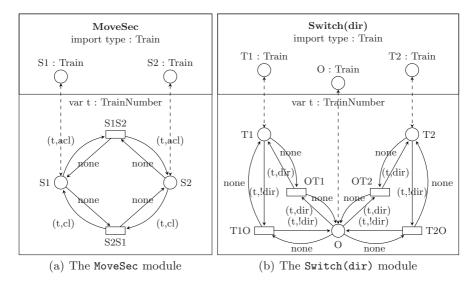

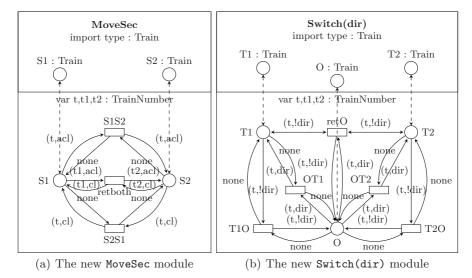

| A Modelling Approach with Coloured Petri Nets                                                   | 73  |

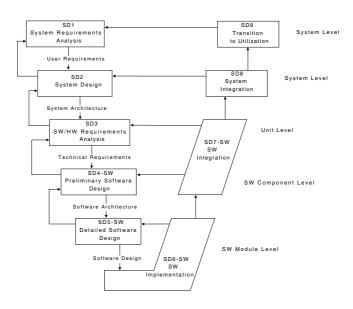

| A Tailored V-Model Exploiting the Theory of Preemptive Time Petri Nets                          | 87  |

| Concurrent Program Metrics Drawn by Quasar                                                      | 101 |

| A Comparison of the Object-Oriented Features of Ada 2005 and Java <sup>TM</sup>                 | 115 |

| A Framework for CFG-Based Static Program Analysis of Ada<br>Programs                            | 130 |

| A Type-Safe Database Interface                                                                  | 144 |

| StateML <sup>+</sup> : From Graphical State Machine Models to Thread-Safe Ada Code              | 158 |

| Diego Alonso, Cristina Vicente-Chicote, Juan A. Pastor, and<br>Bárbara Álvarez                  |     |

# XIV Table of Contents

| Experience in the Integration of Heterogeneous Models in the Model-driven Engineering of High-Integrity Systems | 171 |

|-----------------------------------------------------------------------------------------------------------------|-----|

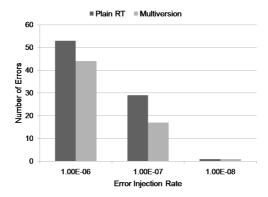

| A Systematic Approach to Automatically Generate Multiple<br>Semantically Equivalent Program Versions            | 185 |

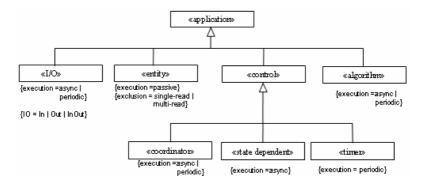

| Increasing Confidence in Concurrent Software through Architectural Analysis                                     | 199 |

| Fast Scheduling of Distributable Real-Time Threads with Assured End-to-End Timeliness                           | 211 |

| RCanalyser: A Flexible Framework for the Detection of Data Races in Parallel Programs                           | 226 |

| Can We Increase the Usability of Real Time Scheduling Theory? The Cheddar Project                               | 240 |

| An Ada 2005 Technology for Distributed and Real-Time Component-Based Applications                               | 254 |

| Real-Time Distribution Middleware from the Ada Perspective                                                      | 268 |

| Author Index                                                                                                    | 283 |

# A New Approach to Memory Partitioning in On-Board Spacecraft Software\*

Santiago Urueña, José A. Pulido, Jorge López, Juan Zamorano, and Juan A. de la Puente

Universidad Politénica de Madrid (UPM), E28040 Madrid, Spain {suruena,pulido,jorgel,jzamorano,jpuente}@dit.upm.es http://www.dit.upm.es/rts/

Abstract. The current trend to use partitioned architectures in onboard spacecraft software requires applications running on the same computer platform to be isolated from each other both in the temporal and memory domains. Memory isolation techniques currently used in Integrated Modular Avionics for Aeronautics usually require a Memory Management Unit (MMU), which is not commonly available in the kind of processors currently used in the Space domain. Two alternative approaches are discussed in the paper, based on some features of Ada and state-of-the art compilation tool-chains. Both approaches provide safe memory partitioning with less overhead than current IMA techniques. Some footprint and performance metrics taken on a prototype implementation of the most flexible approach are included.

**Keywords:** Ravenscar Ada, high-integrity, hard real-time, embedded systems, integrated modular avionics.

#### 1 Introduction

On-board embedded computers play a crucial role in spacecraft, where they perform both platform control functions, such as guidance and navigation control or telemetry and tele-command management, and payload specific functions, such as instrument control and data acquisition. One distinctive characteristic of on-board computer systems is that computational resources are scarce, due to the need to use radiation-hardened hardware chips and also to weight and power consumption constraints. In this kind of systems, the more computational resources on-board the higher energy consumption, which in turn results in more power cells and thus more weight, increasing the total weight and the costs required to launch the spacecraft. Another key aspect of these systems is the presence of high-integrity and hard real-time requirements, which raises the need for a strict verification and validation (V&V) process both at the system and software levels [1].

<sup>\*</sup> This work has been funded in part by the Spanish Ministry of Education, project no. TIC2005-08665-C03-01 (THREAD), and by the IST Programme of the European Commission under project IST-004033 (ASSERT).

F. Kordon and T. Vardanega (Eds.): Ada-Europe 2008, LNCS 5026, pp. 1-14, 2008.

<sup>©</sup> Springer-Verlag Berlin Heidelberg 2008

Current trends envisage systems with increased functionality and complexity. Such systems are often composed of several applications that may have different levels of criticality. In such a scenario, the most critical applications must be isolated from the less critical ones, so that the integrity of the former is not compromised by failures occurring in the latter. Isolation has often been achieved by using a federated approach, i.e. by allocating different applications to different computers. However, the growth in the number of applications and the increasing processing power of embedded computers foster an *integrated* approach, in which several applications may be executed on a single computer platform. In this case, alternate mechanisms must be put in place in order to isolate applications from each other. The common approach is to provide a number of logical partitions<sup>1</sup> on each computer platform, in such a way that each partition is allocated a share of processor time, memory space, and other resources. Partitions are thus isolated from each other both in the temporal and spatial domains. Temporal isolation implies that a partition does not use more processor time than allocated, and spatial isolation means that software running in a partition does not read or write into memory space allocated to another partition.

This approach has been successfully implemented in the aeronautics domain by so-called Integrated Modular Avionics (IMA) [2]. While IMA is industrially supported and effectively provides temporal and spatial isolation, its use in spacecraft systems raises some problems due to the need of complex computer boards that call for alternative, more flexible solutions. In this context, Ada 2005 [3] provides a new set of real-time mechanisms that open the way to new approaches to inter-partition isolation. Some strategies for providing temporal isolation using the new Ada execution-time monitoring mechanisms have already been developed by the authors [4], and prototype implementations have been built in the framework of the ASSERT project<sup>2</sup> [5].

This paper presents new research directed at providing spatial isolation based on alternative approaches to current IMA architectures, including features of the Ada language and operating system-level mechanisms. The basic idea behind the proposed strategies is to modify the compilation toolchain to make a better use of the scarce computational resources at run-time. The available hardware memory protection is still used at run-time, but predictability losses due to address translation in MMUs are avoided. The rest of the paper is organized as follows. Section 2 describes the main aspects of the current IMA architectures. Section 3 introduces some alternative approaches to spatial isolation. Section 4 discusses the architecture of real-time kernels with respect to memory protection, while section 5 details a set of changes needed in the compilation tool-chain needed to implement the two new strategies. Finally, section 6 references some related work, and section 7 summarizes the main conclusions of this paper.

<sup>&</sup>lt;sup>1</sup> Notice that the term *partition* is not used here in the sense defined in the ALRM (10.2/2), but as an implementation of *protection* as specified in the DO-178B (2.3.1).

<sup>2</sup> http://www.assert-project.net/

# 2 Integrated Modular Avionics

Integrated Modular Avionics (IMA) is a generic term to describe an architecture where different avionics applications are executed independently on a single CPU. Applications may have different criticality levels [6], and be logically distributed on different partitions of the same processor or over a network of computers connected by a communication link.

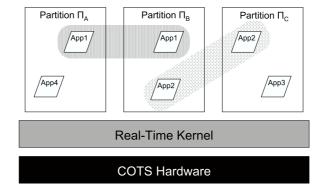

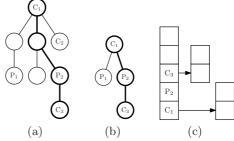

In order to support different criticality levels, applications have to be isolated from each other. Otherwise all the code would have to be certified to the highest criticality, an extremely expensive (and probably impossible) burden. To this purpose, each computer node is divided into one or more partitions, each of which is a virtual container for one or more applications with the same level of criticality, which are isolated in the time and memory domain from applications running in other partitions. An important consequence of partitioning is that applications can be updated individually without requiring re-certification of the whole system. Figure 1 shows an example of an IMA system.

Fig. 1. Four applications with different criticality levels executing inside three partitions over the same computing node

Implementing an IMA architecture requires a specialized operating system layer that provides temporal and spatial isolation between partitions. The AR-INC 653 standard [7] defines an architecture for such an operating system. There are diverse ARINC 653 implementations available from multiple vendors, and the standard has been successfully used in a number of commercial and military avionics systems. However, in spite of its success in the aeronautics field, its application to spacecraft systems raises some problems. First of all, the partition scheduling method is too rigid, and does not allow spare processor time to be re-allocated to other partitions. This may reduce the schedulability of applications on the comparatively slow processors that are currently used in spacecraft computers. The other main problem is that current ARINC 653

implementations require a MMU, which is seldom available on space computers. Indeed, current processors used by ESA<sup>3</sup>, such as LEON2 [8], do not have an MMU. Therefore, other methods not relying on the presence of MMU devices should be explored in order to implement spatial isolation in spacecraft systems.

# 3 Approaches to Spatial Isolation

### 3.1 Static Analysis

SPARK is an Ada-based language designed for high-integrity systems. The language is restricted to a safe subset of Ada, augmented with formal annotations enabling efficient static analysis. A particular kind of annotation refers to the integrity—or criticality—level of program elements, enabling static analysis of violations in the criticality segregation [9]. In this way, static information-flow analysis of source code can be used to guarantee that an application will not write into the memory space of another application.

In principle this method can provide spatial isolation for a node with applications with high criticality levels, and it can also be used to ensure fault containment inside a specific application. However, this approach requires all the software in a computer node to be programmed in SPARK, a language intended only for high-criticality applications. Therefore, it is not suitable for the general case where low-criticality applications, possibly written in other languages, are present. On the other hand, it is an interesting approach to spatial isolation in computers which only host highly critical code, and can also be combined with other methods in a more general situation.

#### 3.2 Run-Time Checks

A second approach is to use the extensive set of compile-time and run-time checks provided by the Ada language to detect possible violations of memory isolation. For example, forbidding using a memory pool in more than one partition seems a reasonable restriction. Following a similar reasoning, the run-time system can be designed so that there is a separate secondary stack for each partition, and an exception is raised in case of overflow. Additional run-time controls for checking that no task can write outside its partition memory area can also be implemented, e.g. when using general access objects a check can be made that the address is inside the partition space, and the same can be done for all access types if 'Unchecked\_Access or Unchecked\_Conversion is allowed.

Wahbe et al [10] proposed a different software technique to avoid writing outside the memory region of the application called *address sandboxing*. Some code is added before dereferencing a pointer which applies a mask to the high bits of the pointer so that the destination address always falls into the memory range of the application. Therefore, even if the pointer is incorrect, the mask ensures

<sup>&</sup>lt;sup>3</sup> European Space Agency.

that it will not write outside its memory region. Address sandboxing does not detect failures, but can be more efficient than run-time checks.

The main problem of these approaches is that they add complexity to the compiler and run time support, which may make it difficult to certify high-criticality applications. They can be retained, however, to implement fault containment regions within a partition.

#### 3.3 Hardware Protection

Some kind of hardware memory protection is available on virtually all processors, usually allowing read and write access, read-only access, or completely hiding a memory region. In addition, a memory area can be made non-executable, which is useful if the area contains only data. The memory protection setting cannot be modified when the processor is in user mode, but only in supervisor mode, and thus it can only be changed by the operating system. These mechanisms can thus be used to ensure that applications of mixed criticality can safely run on the same node. Furthermore, only the operating system must be certified to the highest criticality level, as it is the only subsystem that deals with memory protection.

An MMU is not always available in spacecraft computers because it is a complex hardware component with a comparatively high power consumption [11], as its internal cache for translating addresses, the TLB, is usually fully-associative and frequently accessed. Moreover, the possibility of TLB misses hinders the predictability of the system and introduces some overhead due to address translation and TLB flushes [12]. The complexity of MMU chips also makes them prone to single event upsets (bit flips due to high-energy particles) [2].

There is another main kind of hardware memory protection mechanism, fence registers. Fence registers provide a limited functionality, protecting a fixed number of memory segments of any size. In contrast, an MMU can provide sophisticated memory management schemes, including pagination, segmentation, and virtual memory. While such schemes are usually required in general-purpose operating systems, they are of less use in embedded computing, even with reprogrammability in mind, due to the fact that embedded hard real-time applications are usually statically loaded at system initialization time, at least in spacecrafts. For example, the LEON2 processor has a pair of fence registers that can be used to avoid writings outside the two specified segments of the SRAM.

In this case, there is no hardware relocation, and therefore all applications share a single address space. Memory reads are always allowed by the fence registers. This limits their usefulness as a spatial isolation mechanism, as attempts to read or execute outside the allowed memory area are not detected. In spite of this limitation, fence registers are a simple and robust mechanism without the complexity and comparatively high power consumption of MMUs. Two schemes for implementing spatial isolation based on generic fence registers are described in the following sections.

#### 4 Kernel Architecture

#### 4.1 Architecture of Current Real-Time Kernels

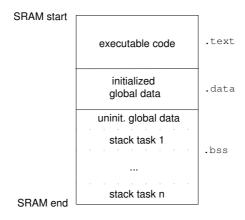

The current practice in the space domain is to execute all the embedded software in supervisor mode, i.e. any application and not only the kernel can execute privileged instructions. Furthermore, all the code executes inside a single (flat) memory space, and all the applications are linked statically into a single binary image, also including the real-time kernel, regardless of their criticality. As shown in figure 2, all the executable code is linked into a single .text section, the global variables are located in the .data and .bss sections, and the stack for each thread is created in the .bss section during initialization.

$\mathbf{Fig.}\,\mathbf{2}.$  Current memory map

This model has several advantages, like increased CPU performance and memory footprint reduction. There is no code duplication because all the applications share the same code, including static libraries. The operating system can be simpler, e.g. there is no application loader. However, hardware memory protection cannot be used to provide complete memory isolation because all the global variables are located in the same section (.data or .bss), regardless of their criticality level. Only the task stacks can have some memory protection because they are clearly separated in memory. ORK, RTEMS, and ThreadX are examples of real-time kernels currently used in the European space industry that follow this memory allocation model.

### 4.2 Needed Architectural Changes

Some changes to the above scheme are required in order to implement spatial isolation using fence registers. Specifically, the global data and stacks (and heap, if available) of each partition must be allocated to separate memory areas, so that the kernel can provide write permission only to the data area of the partition of the thread that is currently executing.

An example of a memory map implementing this principle is shown in figure 3. In this figure, the code and data of each partition (including the kernel) are grouped into dedicated memory zones. Other schemes are possible, for example one with all the executable code in an adjacent area, which can be more efficient as only one segment has to be used for protecting non-executable memory.

| SRAM start |              |                  |

|------------|--------------|------------------|

| 0 0        | .text        | Kernel           |

|            | .data        | Remei            |

|            | .text        | Shared library 1 |

|            | .text        |                  |

|            | .data        |                  |

|            | stack task 1 | Partition 1      |

|            | stack task n |                  |

|            | .text        |                  |

|            | .data        | Partition N      |

|            | stack task 1 |                  |

| SRAM end   | stack task n | -                |

|            |              |                  |

Fig. 3. Memory map for spatial isolation

It should be noticed that the code shared among partitions is compiled as shared libraries, i.e. each partition using a specific shared library reserves in its private data section the space required for the global variables of the shared library. Otherwise, the code would be duplicated in each partition thus increasing the memory footprint. In addition, it is worth noting that some free memory space should be reserved for on-line reprogrammability.

The above schemes show that implementing spatial isolation with fence register requires changes not only in the real-time kernel, but in the compilation and linking process as well. These changes are discussed in the next section.

# 5 Modifying the Compilation Toolchain

#### 5.1 Basic Considerations

In order to implement a partitioned system, the tasks and global data that are included in each partition must be identified in the first place. Possible communication between co-operating applications running on different partitions must also be analysed. This in turn requires some kind of inter-partition communication mechanism to be defined.

In the following paragraphs two alternative strategies for developing partitioned systems are explored. The first one is based on building a custom *linking* script for the partitioned system, and the second one uses a new tool called meta-linker. In both cases the compilation model and the linking method that

are used to produce the executable code are modified with respect to the basic model described in section 4.

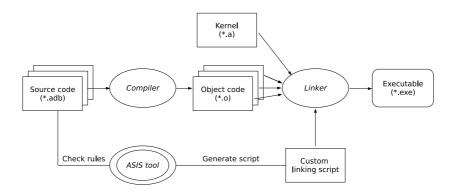

### 5.2 Custom Linking Script

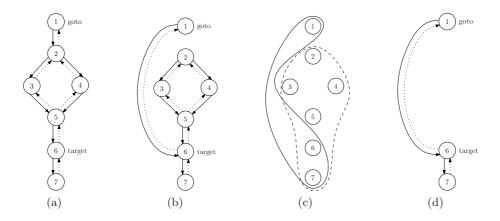

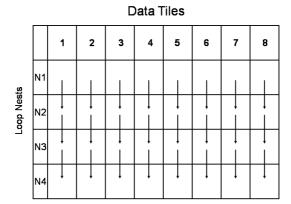

Compilation model. The current practice when using common compilation toolchains is to have all applications in the same computer node compiled as a single Ada program. Spatial isolation can be achieved if all applications are programmed according to a set of rules that clearly mark the tasks and data belonging to each application, e.g. using new pragmas or formal annotations. An ASIS [13] tool can then be used to check the source code and detect possible problems at a system-wide level and to generate a custom script that is used by the linker to produce an appropriate memory map (figure 4).

This approach requires a precise set of Ada rules for partitioning to be defined. Some rules are straightforward, e.g. "tasks belonging to different applications may not be declared in the same package", but some others are more complex, e.g. those on data types transmitted to other applications in order to avoid cross-partition pointers. Overall, a set of rules similar to the Ada Distributed Systems Annex (DSA) [3, App. E] can be defined, with the difference that the run-time system can be shared among all the partitions in the same computer node.

Protected objects (marked with a specific pragma) can be used for interpartition communication (note again footnote 1). Such objects are located in a specific shared memory region, independent of those allocated to partitions. However, when the *proxy-model* implementation of protected objects is used (as in e.g. GNAT), a task can execute some entry code on behalf of some other task [14]. This means that the proxy task may need to write some results in a stack belonging to another partition. One possible solution is to forbid out parameters in protected entries that are used for inter-partition communication. In this case, the entry is used only for signalling the arrival of an inter-partition message, and a protected procedure is then called to read the data.

Fig. 4. Approach 1: Custom linking-script

Linking method. The linker binds each symbol (subprogram or global data) to a specific memory address [15]. This first approach relies on using an appropriate linking method for partitioning code and data into disjoint memory areas, in order to be able to take advantage of hardware memory protection. This approach also requires the kernel to be slightly modified so that it creates the stack of each thread in the global data area allocated to its partition.

The simplest way to implement this approach is to make an ASIS tool that checks the programming rules and generates a custom *linking script* for the system. The script specifies the location of each piece of data and each memory stack according to the partition it belongs to. The linker uses this custom script to generate an executable image with code and data allocated to the specified areas and symbol resolution (see figure 4).

An important advantage of this strategy is that existing response time analysis techniques can still be used. However, a new set of complex programming rules needs to be defined in order to provide partitioning among applications, and some of them may not be amenable to efficient static checking. In addition, the tool must support all the programming languages used in the system, which may be infeasible in some cases.

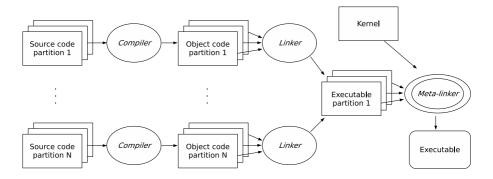

#### 5.3 Meta-Linker

Compilation model. The second strategy for memory isolation is based on compiling each partition as a separate Ada program, with all its tasks and global data belonging to that partition. Task priorities are global, i.e. the scheduler does not have any notion of partitions. On the other hand, no global variables can be shared among partitions. Hence, a new kernel service for inter-partition communication, similar to a message queue, has to be implemented. This service can be specially crafted to be very efficient in CPU time and memory space. Only one-way communication is needed, so blocking time can be minimized with respect to intra-partition synchronization primitives. The main requirement is that inter-partition communications must be predictable so that response time analysis can still be performed.

Fig. 5. Approach 2: Meta-linker

The problem with this approach is how to perform application-wide analysis with applications running in multiple partitions. Since there are no global shared data, the Ada Distributed Systems Annex can be used as a basis. Notice that the DSA also supports partition-wide strong typing enforcing by the compiler. The DSA is designed so that each partition has a separate run-time system. However, in this case the run-time can be shared among all partitions in order to reduce memory footprint. Distribution transparency is achieved as any partition can be moved to another node without source code modification. Therefore Ada provides all the needed support, and there is no need for language extensions like new pragmas as in the previous approach.

Linking method. Under this approach each partition is first linked separately, but relocation information is retained in a linkable output format (e.g. ELF offers this possibility). Then a new tool called *meta-linker* finally sets the memory area of each partition, the kernel, and all shared libraries (including the Standard Ada Libraries) into a single executable. The data of each partition are bound to a separate location by the meta-linker so hardware memory protection can be used, taking into account the size and alignment requirements. The meta-linker also creates some data structures describing the layout of the partition. This information is needed by the kernel to adjust the fence registers in each context switch.

The meta-linker can be seen as an alternative to the address translation performed by an MMU, although in this case the address translation is performed statically within the compilation chain. It can be simple enough to be a qualified tool [6, §12.2], and therefore there is no need to certify again all the partitions if a change in the size of one of them results in modifying their base addresses.

It is often required that a partition can be independently modified without a need for re-linking and re-certifying other partitions. This can be done in two ways. The first one is that the linker resolves all symbols with an arbitrary base address, retaining all the relocation information for each symbol in the object code. The meta-linker adjusts the base address of all symbols for each partition at the time of building the final executable. The alternative is to generate Position Independent Code (PIC), so that the meta-linker only needs to adjust some symbols and specific pointers to global data. The problem with the first solution is that it makes the meta-linker more complex, and it also may require some changes in the compiler and linker, this making qualification more difficult. On the other hand, compiling as PIC often leads to larger and slower code, which may be a problem when computing resources are scarce.

### 5.4 Prototyping

In order to evaluate performance penalties, a meta-linker prototype and a new version of GNAT/ORK for LEON (a variant of GNAT<sup>4</sup> which uses an evolved version of the ORK kernel [16]), which can generate PIC, have been built.

The first problem that has been investigated is a potential increase in footprint. Preliminary measurements have been taken in order to evaluate the

<sup>4</sup> http://www.adacore.com/

differences between PIC and non-PIC executables. Compiling both synthetic benchmarks and real code used in space projects, the increase in the number of instructions can be considered tolerable for this type of embedded systems. The size increase of the executable code (.text section) has been found to be about 7-15%, and the penalty in the total memory usage is only 1-4%, including also the data and stack segments, as shown in table 1.

|               | Executable code    |         | Global data |        | Stacks            |         |                    |

|---------------|--------------------|---------|-------------|--------|-------------------|---------|--------------------|

|               | non-PIC            | PIC     | non-PIC     | PIC    |                   | non-PIC | PIC                |

| Benchmark 1   |                    |         |             |        |                   |         |                    |

| Benchmark 2   |                    |         |             |        |                   |         |                    |

| Application 1 |                    |         |             |        |                   |         |                    |

| Application 2 | $1060~\mathrm{KB}$ | 1134 KB | 599 KB      | 610 KB | $320~\mathrm{KB}$ | 1979 KB | $2064~\mathrm{KB}$ |

Table 1. Footprint increase of Position Independent Code (PIC)

Position Independent Code (PIC) also has an execution time penalty when calling to a function in a shared library or referring to a global variable. As the linker cannot know where the code will be loaded, non-static routines must be called via a Procedure Linkage Table (PLT) and two actual jumps are performed instead of just one as usual. In order to measure the negative impact on performance, a set of composite benchmarks and high-level algorithms from the Performance Issue Working Group (PIWG) test suite were used. Table 2 shows the results which for the Dhrystone and Whetstone benchmarks, as well as three complex algorithms. The significant differences are just in the Dhrystone and Whetstone benchmarks, as the differences in the high level algorithm tests and other PIWG tests are negligible or even favour PIC.

The most significant difference is in the Dhrystone benchmarks with full optimization where the performance penalty of PIC is about 38%. The penalty is about 21% for this test with no optimization. However, the Dhrystone benchmark consists of composite calls to integer routines with a very short execution time. Conversely, the Whetstone benchmark routines perform floating point calculations with considerably longer execution times. In this cases, the penalty ranges from 0.5% to 4.5%. Of course, a program calling mostly short routines will pay a comparatively higher penalty due to extra jumps.

The real situation is likely to be closer to the high level algorithms, where the maximum penalty is about 12%, and the minimum one is negligible. Therefore, it can be said that the penalty of using PIC is acceptable both in footprint and performance for typical real situations. It must be noticed that using an MMU approach for spatial isolation also pays a significant performance penalty due to heavier context switches.

In summary, it can be said the best way to provide spatial isolation based on fence registers as the only hardware support is the second proposed strategy, i.e. writing separate source code for each application and compiling and linking each partition separately, keeping the relocation information. A qualified metalinker is then used to examine the sizes of the kernel, the shared libraries, and

| Description                           | No optimization non-PIC PIC |                    | Full optimization non-PIC PIC |                     |

|---------------------------------------|-----------------------------|--------------------|-------------------------------|---------------------|

| Dhrystone                             | $91.50 \ \mu s$             | $111.52 \ \mu s$   | $30.56 \ \mu s$               | $41.66 \ \mu s$     |

| Whetstone manufacturers math routines | 228.00 ms                   | 233.50 ms          | 128.62 ms                     | 131.88 ms           |

| Whetstone with built-in math routines | 207.76  ms                  | 208.76  ms         | $66.68~\mathrm{ms}$           | 69.56  ms           |

| NASA Orbit determination              | 586.00 ms                   | 635.50  ms         | 281.50  ms                    | 316.50 ms           |

| JIAWG Kalman benchmark                | 185.76  ms                  | 186.00  ms         | $20.28~\mathrm{ms}$           | $20.18~\mathrm{ms}$ |

| Tracker centroid algorithm            | $5.64~\mathrm{ms}$          | $5.58~\mathrm{ms}$ | $2.08~\mathrm{ms}$            | $2.08~\mathrm{ms}$  |

Table 2. Comparison in execution time

the partitions, adjust the base address of the whole application, and generate a single binary image. Finally, the real-time kernel adjusts the fence registers and processor mode at run time in order to provide the required strong hardware memory protection between partitions.

This is an elegant and powerful solution as it enables distributed applications (e.g. using a specialized DSA implementation) to be written in any programming language, including Ravenscar Ada and SPARK for high-criticality applications, or full Ada and C for low-criticality ones. It enables the performance and predictability problems of an MMU to be avoided, and allows individual partitions to be modified without having to certify again the whole system.

No modifications are required to current compilers, assemblers, or linkers, and the meta-linker is designed to be simple enough to be qualified for the development of high-integrity software. Furthermore, no extensions are required to the Ravenscar profile for enabling spatial isolation using the meta-linker approach. The few and localized additions to the kernel are not expected to hinder certification, being less complex or at least comparable to the software implementation support required by an MMU.

#### 6 Related Work

The implications of the MMU in Integrated Memory Avionics have also been studied by Audsley and Bennet [12]. Using SPARK for mixed criticality high-integrity systems was proposed by Amey and others [9].

The performance penalties with respect to Position Independent Code have been analysed by several authors. However, measurements comparing PIC and non-PIC executables for embedded systems are not easy to find. One example of measurements for general purpose C++ applications is presented by Hamilton [17].

Other industrial domains could take advantage of the proposed techniques for achieving spatial isolation. For example, Autosar [18] is an automotive standard with a similar objective as Integrated Modular Avionics. The target CPUs used in those systems do not usually have an MMU, and therefore the standard does not consider spatial isolation. However, some of the techniques proposed in this paper can be a solution to provide memory protection on such systems.

### 7 Conclusions

Spatial isolation is needed to comply with the requirements of the the next-generation systems in the aerospace domain. A Memory Management Unit is commonly used for this purpose in general purpose operating systems, but performance and predictability problems appear when using MMUs in hard real-time embedded systems. Indeed, processors currently used in the European space industry an other embedded application domains, only include basic memory protection mechanisms, such as fence registers.

Several techniques have been explored in order to find a memory isolation scheme that can be used in this type of systems, most of them taking advantage of the unique characteristics of the Ada language. The recommended approach for systems composed only of high-integrity code is to use a safe subset of the language, such as SPARK, which also enables the absence of errors to be statically proved under appropriate conditions.

For systems composed of high- and low-criticality applications, a novel and powerful solution, involving a separate compilation of each partition, and a qualified meta-linker to generate the final executable, has been proposed. This flexible approach provides the same features as traditional techniques like strong memory partitioning, independent certification of partitions and maintenance, but it requires less hardware functionality and adds less overhead as specific processing is done statically at build time. Finally, additional Ada run-time checks can be used to detect programming errors inside each partition. A special-purpose implementation of the Ada Distributed Systems Annex can be used to enable static program-wide analysis of applications spanning multiple partitions, a characteristic which is often required for the certification of high-integrity systems.

A meta-linker prototype has been implemented as a proof of concept of the whole approach. The tool is simple enough to be qualified to a high-integrity level, and experimental performance and footprint metrics show that there is not a substantial penalty if the partitions are compiled as Position Independent Code. No modifications are required to the compiler, assembler or linker.

Future work includes specific compiler modifications to improve the generation of position independent code for embedded platforms, and research about how to reduce the impact of processor mode changes in space processors.

#### References

- 1. ECSS: ECSS-Q-80B Space Product Assurance Software Product Assurance. Available from ESA (2003)

- Rushby, J.: Partitioning for safety and security: Requirements, mechanisms, and assurance. NASA Contractor Report CR-1999-209347, NASA Langley Research Center (June 1999) Also to be issued by the FAA

- 3. Tucker Taft, S., Duff, R.A., Brukardt, R.L., Plödereder, E., Leroy, P.: Ada 2005 Reference Manual. LNCS, vol. 4348. Springer, Heidelberg (2006)

- 4. Pulido, J.A., Urueña, S., Zamorano, J., de la Puente, J.A.: Handling Temporal Faults in Ada 2005. In: Abdennahder, N., Kordon, F. (eds.) Ada-Europe 2007. LNCS, vol. 4498, pp. 15–28. Springer, Heidelberg (2007)

- Zamorano, J., de la Puente, J.A., Hugues, J., Vardanega, T.: Run-time mechanisms for property preservation in high-integrity real-time systems. In: OSPERT 2007 — Workshop on Operating System Platforms for Embedded Real-Time Applications, Pisa. Italy (July 2007)

- RTC: RTCA SC167/DO-178B Software Considerations in Airborne Systems and Equipment Certification (1992); Also available as EUROCAE document ED-12B

- ARINC: Avionics Application Software Standard Interface ARINC Specification 653-1 (October 2003)

- 8. Gaisler Research: LEON2 Processor User's Manual (2005)

- 9. Amey, P., Chapman, R., White, N.: Smart Certification of Mixed Criticality Systems. In: Vardanega, T., Wellings, A.J. (eds.) Ada-Europe 2005. LNCS, vol. 3555, pp. 144–155. Springer, Heidelberg (2005)

- 10. Wahbe, R., Lucco, S., Anderson, T.E., Graham, S.L.: Efficient software-based fault isolation. ACM SIGOPS Operating Systems Review 27(5), 203–216 (1993)

- 11. Chang, Y.J., Lan, M.F.: Two new techniques integrated for energy-efficient TLB design. IEEE Transactions on Very Large Scale Integration (VLSI) Systems 15(1), 13–23 (2007)

- 12. Bennett, M.D., Audsley, N.C.: Predictable and efficient virtual addressing for safety-critical real-time systems. In: Proceedings of the 13th Euromicro Conference on Real-Time Systems (ECRTS 2001), pp. 183–190. IEEE Computer Society Press, Los Alamitos (2001)

- 13. ISO: Ada Semantic Interface Specification (ASIS). ISO/IEC- 15291:1999 (1999)

- Giering, E.W., Baker, T.P.: Implementing Ada protected objects—interface issues and optimization. In: TRI-Ada 1995: Proceedings of the conference on TRI-Ada 1995, pp. 134–143. ACM Press, New York (1995)

- 15. Levine, J.R.: Linkers and Loaders. Morgan Kaufmann, San Francisco (2000)

- Urueña, S., Pulido, J.A., Redondo, J., Zamorano, J.: Implementing the new Ada 2005 real-time features on a bare board kernel. Ada Letters XXVII(2), 61–66 (2007); Proceedings of the 13th International Real-Time Ada Workshop (IRTAW 2007)

- 17. Hamilton, G., Nelson, M.N.: High performance dynamic linking through caching. Technical report, Sun Microsystems, Inc., Mountain View, CA, USA (1993)

- 18. Heinecke, H., Schnelle, K.P., Fennel, H., Bortolazzi, J., Lundh, L., Leflour, J., Maté, J.L., Nishikawa, K., Scharnhorst, T.: AUTomotive Open System Architecture an industry-wide initiative to manage the complexity of emerging Automotive E/E-Architectures. In: Convergence 2004 (2004)

# Design and Development of Component-Based Embedded Systems for Automotive Applications

Marco Di Natale

Scuola Superiore S. Anna, Pisa, Italy marco@sssup.it

Abstract. Automotive software systems are characterized by increasing complexity, tight safety and performance requirements, and need to be developed subject to substantial time-to-market pressure. Model-and component-based design methodologies can be used to improve the overall quality of software systems and foster reuse. In this work, we discuss challenges in the adoption of model-based development flows, and we review recent advances in component-based methodologies, including existing or upcoming standards, such as the MARTE UML profile, ADL languages and AUTOSAR. Finally, the paper provides a quick glance at results on a methodology based on virtual platforms and timing analysis to perform the exploration and selection of architecture solutions.

#### 1 Introduction

The automotive domain is experiencing evolutionary changes because of the demand for new advanced functions, technological opportunities and challenges, and organizational issues. The increased importance and value of electronics systems and the introduction of new functions with unprecedented complexity, timing and safety issues are changing the way systems are designed and developed and are bringing a revolution in the automotive supply chain. New standards and methodologies are being developed that will likely impact not only automotive electronics systems, but also other application domains, which share similar problems.

The automotive supply chain is currently structured in tiers

- Car manufacturers (or Original Equipment Manufacturers OEMs).

- Tier 1 suppliers who provide electronics subsystems to OEMs.

- *Tier 2 suppliers* e.g., chip manufacturers, IP providers, RTOS, middleware and tool suppliers, who serve OEMs and more likely Tier 1 suppliers.

- Manufacturing suppliers providing manufacturing services.

Currently, automotive systems are an assembly of *components* that are designed and developed in house or, more often, by Tier 1 suppliers. These subsystems have traditionally been loosely interconnected, but the advent of active-safety and future safety-critical functions, including by-wire systems, and the interdependency of these functions is rapidly changing the scenario. Furthermore,

F. Kordon and T. Vardanega (Eds.): Ada-Europe 2008, LNCS 5026, pp. 15-29, 2008.

<sup>©</sup> Springer-Verlag Berlin Heidelberg 2008

subsystems are developed using different design methods, software architectures, hardware platforms, real-time operating systems and middleware layers. To give an idea of architecture complexity, the number of Electronic Control Units (ECUs) in a vehicle is presently in the high tens, and further increasing. In the face of this scenario, OEMs need to understand and control the emerging behavior of the complex distributed functions, resulting from the integration of subsystems. This includes both functional and para-functional properties, such as timing and reliability. The supply process, traditionally targeted at simple, black-box integrated subsystems, will evolve from the current situation, where the specifications issued to the OEMs consist of the message interface and general performance requirements, to more complex component specifications that allow plug-and-play of portable software sub-systems.

The essential technical problem to solve for this vision is the establishment of standards for interoperability among IPs, both software and hardware, and tools. AUTOSAR [1], a world-wide consortium of almost all players in the supply chain of automotive electronics, has this goal very clear in mind. However, several issues need to be solved for function partitioning and subsystem integration, in the presence of real-time and reliability requirements, including:

- Composability and refinement of subsystems. The automotive industry together with the avionic industry was the first to embrace model-based design, as a tool to remove coding errors and to speed up the software development process. This approach was made possible by the introduction of powerful simulation tools where the functionality of the system is captured with a mathematically-oriented formalism, such as Simulink [12]. However, the definition of a process that goes from system-level to component models, in which behaviors are formally and unambiguously defined, such that they can verified at design time, and that allows for automatic code generation, is a quite challenging task. Such a process would indeed require that all relevant functional and non-functional constraints and properties are captured by the models used at all levels and that model semantics is preserved at each refinement/transformation steps. In Section 2 we discuss the issues related to model-based development and we review the impact of AUTOSAR on the design methodology.

- Time predictability. This issue is related to the capability of predicting the system-level timing behavior (latencies and jitter), resulting from the synchronization between tasks and messages, but also from the interplay that different tasks can have at the RTOS level and the synchronization and queuing policies of the middleware. The timing of end-to-end computations depends, in general, on the deployment of the tasks and messages on the target architecture and on the resource management policies. In Section 3, we review issues in this domain.

- Dependability. The deployment of the functions onto the ECUs and the communication and synchronization policies must be selected to meet dependability targets. A system-level design tool should integrate support for design patterns suited to the development of highly-reliable systems with

fault containment both at the functional level and at the timing level. Such tools should also support the automatic construction of fault-trees to compute the probability of a hazard occurrence.

Complex automotive functions, including active-safety and safety-critical systems, are characterized by non-functional requirements, including timing and performance, requirements for safety, and cost, together with reusability and extensibility of the architecture artifacts. System-level analysis and new modeling and analysis methods and tools are not only needed for predictability and composability when partitioning end-to-end functions, but also for providing guidance and support in the evaluation and selection of the electronics and software architectures. In Section 4, we provide the description of a design methodology based on virtual platforms in which models of the functions and of the possible solutions for the physical architecture are defined and matched to select the best possible hardware platform with respect to performance. Opportunities for the automatic synthesis of the software architecture are also discussed.

### 2 Model-Based Design, Composability and AUTOSAR

Model-based design methodologies are increasingly adopted for improving the quality and the reusability of software. A model-based environment allows the development of control and dataflow applications in a graphical language that is familiar to control engineers and domain experts. The possibility of defining components (subsystems) at higher levels of abstraction and with well defined interfaces allows separation of concerns and improves modularity and reusability. Furthermore, the availability of verification tools (often by simulation) gives the possibility of a design-time verification of the system properties. However, when considered in the context of a design flow that starts from the early stages of architecture exploration and analysis and supports complex interacting functions with real-time requirements, deployed on a distributed architecture, most modern tools for model-based design have a number of shortcomings

Lack of separation between the functional model and the architecture model: such a separation is fundamental for exploring different architecture options with respect to a set of functionality and for reusing an architecture platform with different functions.

Lack of support for the definition of the task and resource model: Most model-based flows support the transition from the functional model directly to the code implementation. The designer has limited control on the generation of the task set and the task and resource model is scantly addressed. Placement of tasks in a distributed environment is typically performed at the code level. The specification of the task and message design and of the resource allocation is necessary to evaluate the timing and dependability properties of the system.

Insufficient support for the specification of timing constraints and attributes: The definition of end-to-end deadlines, as well as jitter constraints is often not considered by modeling languages.

Lack of modeling support for the analysis and the back-annotation of scheduling-related delays: Most tools support simulation and verification of the functional model, which is typically based on an assumption of zero communication and computation delays. The definition of the deployment on a given architecture allows the analysis of the delays caused by resource sharing. In a sound design flow, tools should support this type of analysis, and the communication and scheduling delays should be back-annotated into the model to verify the performance of the function on a given architecture solution.

Issue of semantics preservation: The generation of the code starting from a model description is not always performed in such a way that the original semantics is preserved. It is important that designers and developers understand under what conditions the code generation stage can preserve the model semantics and what are the implications of an incorrect implementation.

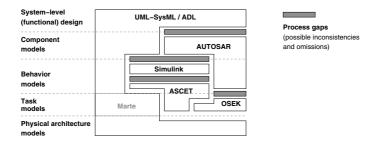

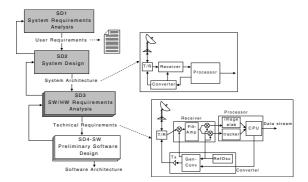

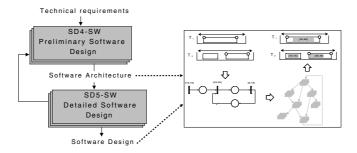

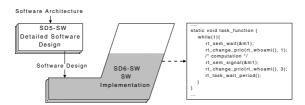

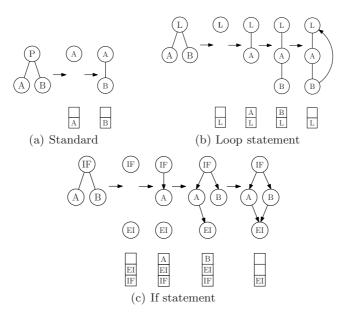

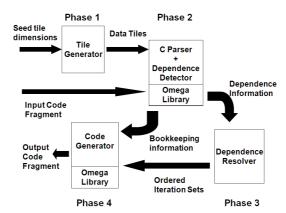

Some of these issues can be reviewed in more detail, with reference to an abstract design flow, which encompasses all the refinement steps, from the system-level view, down to the code implementation (Figure 1).

Fig. 1. An abstract development flow: standards and process gaps

The highest level in the description of the system corresponds to the early decomposition of high-level end-to-end functions (typically derived from user requirements). The system description is characterized by a behavior specification, but also by reliability and time requirements. Candidate languages and standards for system-level modeling, which may include a first-level decomposition into major functional blocks or subsystems, are the Unified Modeling Language (UML) and its specialized profile SysML, and Architecture Description Languages (ADL), like the EAST/ADL [22].

In order to allow for the specification and modeling of time and reliability requirements, UML has recently been extended by two profiles (specialized restrictions of the language semantics), the MARTE profile for the specification of timing requirements and properties [20] and the UML Profile for Modeling QoS and Fault Tolerance Characteristics and Mechanisms [21]. Both standards are expected to provide support for expressing time and reliability properties and requirements. However, because of the need of dealing with the generality of the UML language, they are typically cumbersome (the MARTE profile

specification is currently 658 pages long) and must rely on faithful and efficient implementation by tool vendors, which presently cannot be guaranteed.

Subsystem specifications are then passed from OEMs to Tier-1 suppliers, who are responsible for their development. Although UML can still be used at this stage, the AUTOSAR development partnership [1], including several OEM manufacturers, Tier-1 suppliers, tool and software vendors, has been created with the purpose of developing an open industry standard for component specification and later integration.

To achieve the technical goals of modularity, scalability, transferability and re-usability of functions, AUTOSAR provides a common software infrastructure based on standardized interfaces for the different layers. The current version of the AUTOSAR model includes a reference architecture and interface specifications. AUTOSAR has been focused on the concepts of location independence, standardization of interfaces and portability of code. While these goals are undoubtedly of extreme importance, their achievement is not a sufficient condition for improving the quality of software.

The current specification has at least two major shortcomings. The AU-TOSAR metamodel, as of now, is affected by the lack of a clear and unambiguous communication and synchronization semantics and the lack of a timing model. The AUTOSAR consortium recently acknowledged that the specification was lacking a formal model of components for design time verification of their properties. As a result, the definition of the AUTOSAR metamodel was started. Similarly to UML, the AUTOSAR metamodel is sufficiently mature in its static or structural part, but offers an often incomplete behavioral description, which is planned for significant updates in its upcoming revision. Furthermore, the standard does not address adequately issues related to timing and performance, therefore underestimating the complexity of current and future applications, in which component interactions generate a variety of timing dependencies due to scheduling, communication, synchronization, arbitration, blocking, buffering. The reuse of a component requires that the behavior of the reused components and the result of the composition with respect to time can be predicted in the new configuration. If this problem is not addressed, the composition will eventually lead to (possibly transient) timing problems. The definition of a timing model for AUTOSAR and the development of a standardized infrastructure for the handling of time specifications is the objective of the ITEA project TIMMO, which started in April 2007 and includes car manufacturers like Audi, PSA, Volvo Technology and Volkswagen, as well as electronics and tool suppliers, including Bosch, Continental, ETAS, Siemens VDO, Symtavision and TTTech.

On a separate context, a discussion of the issues that need to be considered when mapping UML into AUTOSAR (and vice-versa) and the possible gaps and inconsistencies in this transformation can be found in [22].

Components must be characterized by (a set of) behavior requirements and a corresponding internal behavior model. In AUTOSAR, the behavior of Atomic-SoftwareComponents is represented by a set of RunnableEntities (Runnables for short) communicating with each other over the ports of the container structural

entities (components). Like in UML, structural and behavioral entities are linked to each other but are kept separated. AUTOSAR provides several mechanisms for Runnables to access the data items for sender/receiver communication and the services of client/server communication, but the synchronization and timing semantics in the execution of Runnables is only partly specified. In AUTOSAR, the runtime environments (RTEs) of each ECU are responsible for establishing the communication between the Runnables (local or remote) and triggering their execution using the following events:

- Timing Event triggering periodical execution of Runnables.

- DataReceivedEvent upon reception on a Sender/Receiver communication.

- OperationInvokedEvent for invocation of Client/Server service.

- DataSendCompleteEvent upon sending a Sender/Receiver communication.

- WaitPoint allows blocking a runnable while waiting for an Event.

Behavioral models are not supported in AUTOSAR, but the standard relies on external behavioral modeling tools like Simulink and ASCET, which brings the issue of the composition of (possibly heterogeneous) models. Therefore, any integration environment (EAST-ADL2 [22] is an example), must define the triggering and execution semantics of functions. This semantic should be deterministic to allow execution verification.

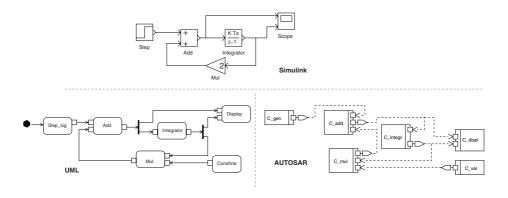

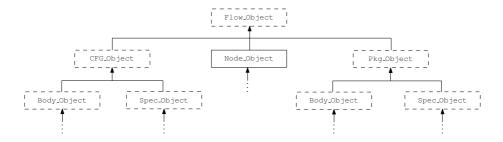

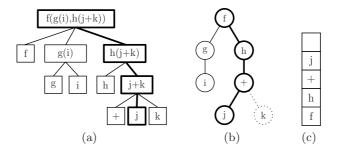

An example of the possible issues in the definition of the execution semantics (and also an example of model translation issues) can be found in Figure 2 (adapted from [22]), in which three models of a control algorithm, respectively in Simulink, UML (activity diagram) and AUTOSAR are represented.

Fig. 2. Model-to-model transformation issues

Despite a similarity in their structure, the three models differ in the execution order of the actions. Contrary to UML activity diagrams, in Simulink, blocks are not executed in lexicographic order. In Simulink, blocks for which the output does not depend on the input at any given time, such as the *Integrator* in the Figure, can be executed before the others. Indeed, the simulation behavior of the depicted Simulink model will start with the output of the *Integrator*, and

then continue with the Mul and Add blocks. In the UML activity diagram, the Add action will run before the Integrator block. The difference in the execution order may lead to different model behaviors and different simulation results.

In UML, in fact, the triggering order is defined when operations are called, but the execution order is undefined in the case of communication by data (streams) received on ports. SysML tries to define the semantics of data reception on ports, but the bindings between behavior parameters, and either the flow properties or the containing block properties are a semantic variation point [22]. In conclusion, for triggering semantics that differ from the loose UML standard definition, designers are required to explicitly define their own semantics by introducing stereotypes (specializing generic UML concepts by additional constraints and tagged values) in a dedicated profile .

However, execution order is not the only problem with our example. In Simulink, all blocks react at the same time and produce outputs in zero time (according to the Synchronous Reactive semantics), which leads to possible problems when the model has algebraic loops (instantaneous cyclic dependencies of signals from themselves). In this case, the system may have a fixed point solution or the model may be simply not correct. The definition of a Synchronous Reactive semantics in UML is probably possible by leveraging the Marte profile, but it would require the adoption of a stereotyped (discrete) time model. Additional diagrams are probably required to synchronize triggers and/or enforcing the correct execution order (possibly state diagrams). Finally, in case other types of timing constraints on end-to-end computations exist, an additional sequence diagram (and a stereotyped notation for timed events) would be required as well.

Finally, the AUTOSAR specification is based on the OSEK specification for Operating Systems. In an OSEK system, tasks are executing concurrently with priorities and subject to preemption. Hence, special care must be taken in the code generation stage, when the structural and behavioral part of the specification are mapped into concurrent tasks using automatic code generation techniques. Runnables and functional blocks must be executed by tasks in such a way to ensure data consistency of the variables implementing the communication links, and also time determinism in the execution of blocks. Furthermore, the implementation must guarantee the enforcement of the set of partial orders in the execution of blocks, as determined by the model semantics.

# 3 Timing Predictability, Timing Isolation and Standards

The automotive domain has been traditionally receptive to methods and techniques for timing predictability and time determinism. The standard Controller Area Network (CAN) bus [6] for communication is based on the concept of a deterministic resolution of the contention and on the assignment of priorities to messages. The OSEK standard for real-time operating systems [14] not only supports predictable priority-based scheduling [10], but also bounded worst-case blocking time through an implementation of the immediate priority ceiling protocol [17] and the definition of non-preemptive groups [18] for a possible further

improvement of some response times and to allow for stack space reuse. In the absence of faults, and assuming that the worst-case execution time of a task can be safely estimated, these standards allow the designer to predict the worst-case timing behavior of computations and communications.

Priority-based scheduling of tasks and messages fits well within the traditional design cycle, in which timing properties are largely verified a-posteriori and applications require conformance with respect to worst-case latency constraints rather than tight time determinism. Furthermore, control algorithms are designed to be tolerant with respect to small changes in the timing behavior and to the nondeterminism in time that possibly arises because of preemption and scheduling delays [7], or even possibly to overwritten data or skipped task and message instances because of temporary timing faults. Finally, although formally incorrect, there is a common perception that small changes in the timing parameters (decreased periods and/or wrong estimates of the computation times) typically only result in a graceful degradation of the response times of tasks and messages and that such degradation will in any case preserve the high priority computations.

These assumptions can be misleading and faulty. The worst-case response times of tasks and messages, scheduled on priority-based systems, such as those defined by the OSEK and CAN standards can be computed using a fixed point formula. For a periodic task  $\tau_i$ , activated with period  $T_i$  and worst-case computation time  $C_i$ , the worst-case response time  $r_i$  is given by (in case  $r_i \leq T_i$ , the general case is discussed in [11])

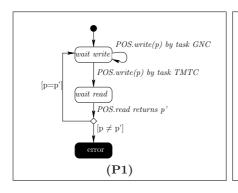

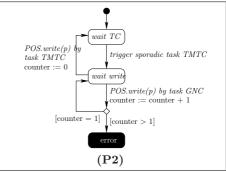

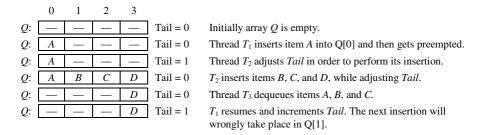

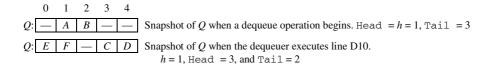

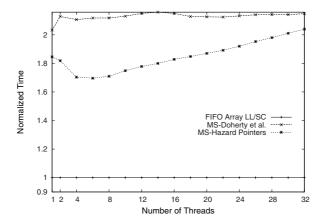

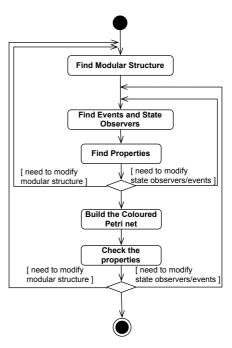

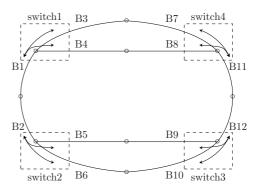

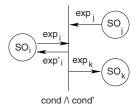

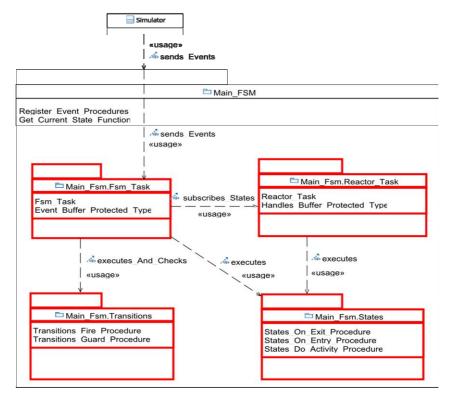

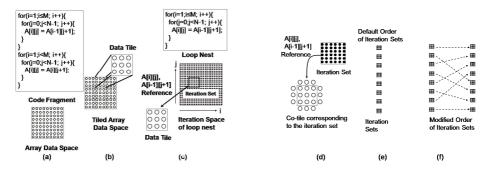

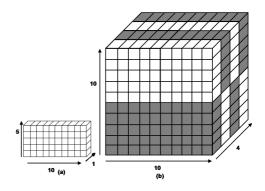

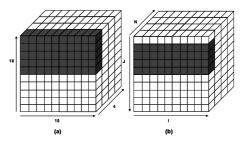

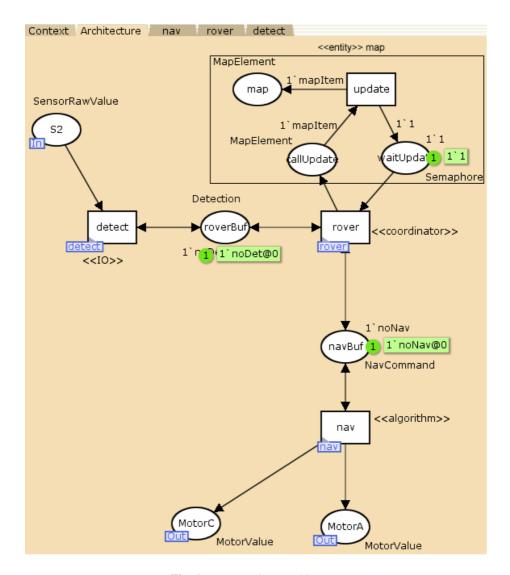

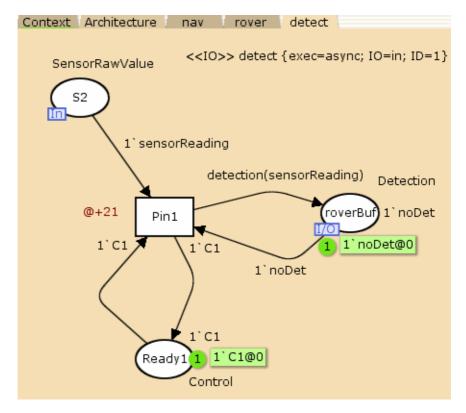

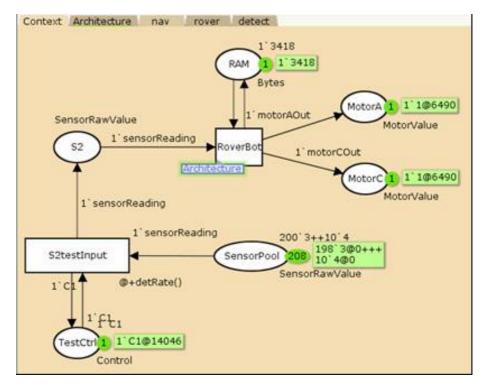

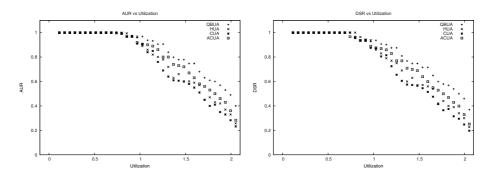

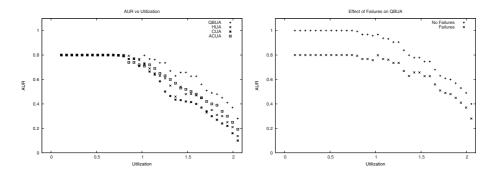

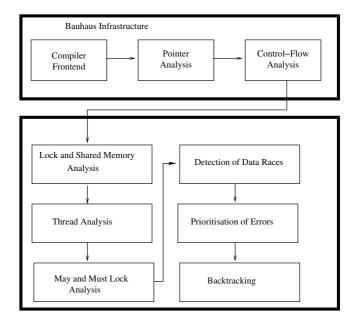

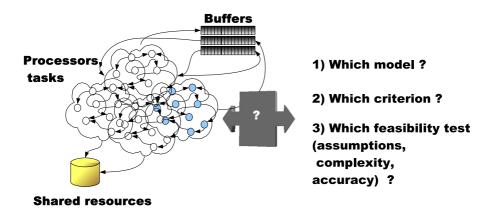

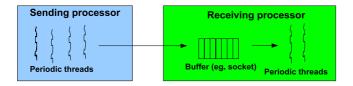

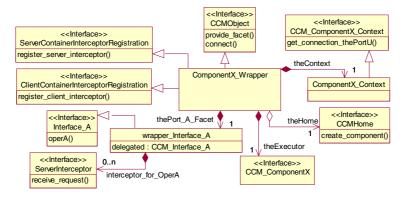

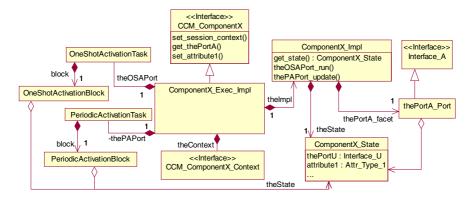

$$r_i = B_i + C_i + \sum_{j \in hp(i)} \left\lceil \frac{T_i}{T_j} \right\rceil C_j \tag{1}$$